|

|

|

|

|

|

| Research Activities of Each Sub-Project |

|

|

|

|

|

[ Visual processing devices and systems ] |

|

|

Sub-project leader : Morie |

|

|

|

|

|

Vision SP

| (1) |

Outline

We are aiming at realizing human-like vision functions exceeding the limit of conventional image processing by developing brain-like vision processing algorithms inspired by the knowledge in vision psychology and neurophysiology. Because brain-like massively parallel processing requires huge computational power, we are developing dedicated large-scale integrated circuit (LSI) chips with high-performance and low-power consumption, and are constructing vision systems using them. These are targeted at applications to intelligent vision for robots and automobiles.

|

| 1) |

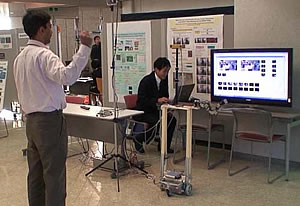

A face and arm-posture recognition system using Gabor filtering LSI and robot control using it

Morie Lab (Device division) and Miyamoto Lab (Modeling and System division) have collaboratively developed a face and arm-posture recognition system, and have demonstrated robot control using recognition results. This system includes a dedicated LSI chip implementing feature extraction using Gabor filtering and a digital LSI (FPGA) chip implementing elastic graph matching. These LSI chips and the face recognition system were partly supported by fund from the MEXT via Kitakyushu innovative cluster project (2002-2006). |

|

| 2) |

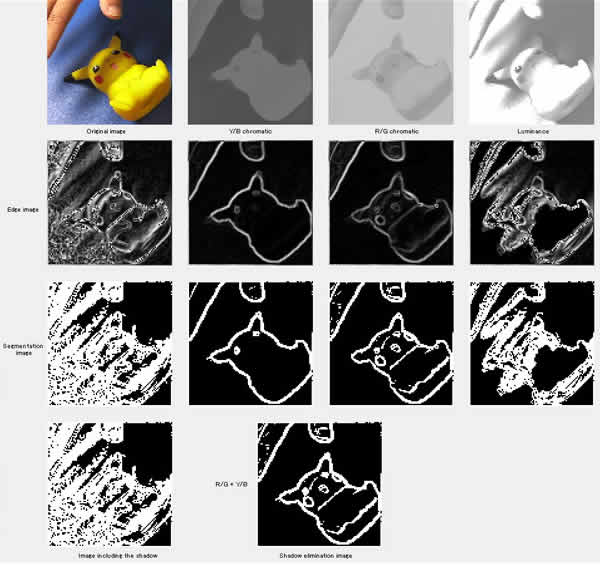

A shadow elimination algorithm and system based on human visual perception mechanism

Prof. Hanazawa (Vision psychology and neurophysiology division) has proposed a shadow elimination algorithm, and has developed a real-time shadow elimination system in collaboration with Morie Lab. This algorithm uses the correlation of chromatic and luminance variations. If chromatic and luminance variations arise at the same place in a visual image, humans recognize the place as the surface color variation of the objects in the image. On the other hand, if only a luminance variation arises at a place, humans recognize the luminance variation as a shadow. |

|

|

|

| (2) |

Members

Prof. Takashi Morie: devices and systems

Prof. Hiroyuki Miyamoto: modeling and systems

Prof. Akitoshi Hanazawa: vision psychology and neurophysiology, modeling

|

|

|

| Page top ↑ |

|

|

|

| Processing results of face and arm-posture recognition system |

|

|

|

|

| Demo of robot control by face and arm-posture recognition system |

|

Gabor-filtering LSI chip designed using merged A/D architecture |

|

|

|

|

| Measurement results of impulse responses obtained using a fabricated Gabor-filtering LSI chip |

|

Feature-extraction LSI board including Gabor-filtering LSI |

|

|

| Page top ↑ |

|

|

| Processing results of shadow elimination system |

|

|

|

|

|

|

| References |

| [1] |

T. Morie, H. Miyamoto, and A. Hanazawa, Brain-inspired Visual Processing for Robust Gesture Recognition, Brain-Inspired IT III, International Congress Series, Vol. 1301, pp. 31-34, Elsevier, 2007.

|

| [2] |

T. Morie, H. Miyamoto, A. Hanazawa, I. R. Khan, T. Kamada, Y. Kuriya, and M. Shimizu, Brain-inspired Visual Processing: Real-time Face Authentication, arm Posture Recognition, and Shadow Elimination, 4th Int. Conf. on Brain-Inspired Information Technology (BrainIT2007), Abst. of BrainIT2007, p. 33, 2007.

|

| [3] |

T. Nakano and T. Morie, An Image Recognition Algorithm Using Relationships between Segmented Coarse Regions, Brain-Inspired IT II, International Congress Series, pp. 241-244, Elsevier, 2006.

|

| [4] |

S. Nagano, T. Morie, T. Nakano, and K. Nakamura, A Real-time Image Processing System Using a Gabor-filtering LSI Realizing Primary Visual Cortex Functions, Joint 3rd Int. Conf. on Soft Computing and Intelligent Systems and 7th Int. Symp. on Advanced Intelligent Systems (SCIS & ISIS 2006), pp. 516-519, 2006.

|

| [5] |

T. Nakano and T. Morie, A Digital LSI Architecture of Elastic Graph Matching and Its FPGA Implementation, Proc. Int. Joint Conference on Neural Networks (IJCNN05), pp. 689-694, 2005.

|

| [6] |

T. Morie, J. Umezawa, and A. Iwata, A Pixel-Parallel Image Processor for Gabor Filtering Based on Merged Analog-Digital Architecture, 2004 Symposium on VLSI Circuits, Digest of Technical papers, pp. 212-213, 2004.

|

|

|

|

|

HOME | Back | Page top ↑

|

|

|

|

|